# Journal of Modern Technology

Vol. 01, No. 02, Dec 2024, pp. 186-196.

Homepage: https://review.journal-of-modern-technology.com

# Reducing Switch Count in a Self-Balancing Nine-Level Switched Capacitor Inverter: A Modified Approach

Lois Anuale 1\*, Osasumwen J. T. Alimikhena 2, Olafuyi Ogunmuyiwa3

- <sup>1\*</sup> Energy Access and Renewable Energy Technology, University of Port Harcourt, Choba, Port Harcourt 500102, Nigeria. E-mail: <a href="mailto:lois.david@earet.uniport.edu.ng">lois.david@earet.uniport.edu.ng</a> & <a href="lois.david@earet.uniport.edu.ng">lois.david@earet.uniport.edu.ng</a> & <a href="lois.david@earet.uniport.edu.ng">lois.david@earet.uniport.ed

- <sup>2</sup> Electrical Electronics Engineering Department, University of Benin City, Benin 300213, Nigeria. E-mail: <a href="mailto:alimikhena@ndphc.net">alimikhena@ndphc.net</a>, ORCID: <a href="https://orcid.org/0009-0004-3102-0781">https://orcid.org/0009-0004-3102-0781</a>

- <sup>3</sup> Electrical Electronics Engineering Department, University of Ibadan, Ibadan 200005, Nigeria. E-mail: <a href="mailto:oogunmuyiwa2363@stu.ui.edu.ng">oogunmuyiwa2363@stu.ui.edu.ng</a>, ORCID: <a href="https://orcid.org/0009-0009-1519-7452">https://orcid.org/0009-0009-1519-7452</a>

### **Article Info**

### Article history:

Received: Dec 10, 2024 Revised: Jan 15, 2025 Accepted: Jan 25, 2025 First Online: Jan 28, 2025

#### Keywords:

Multilevel inverter Total Harmonic Distortion (THD) reduction, Switched capacitor technique Power quality

### **ABSTRACT**

Renewable energy sources are becoming more and more popular to minimize environmental damage while meeting the world's expanding demand for electricity. However, components like DC-AC converters, trans- former/inductor absence operation, front-end DC-DC converters with high gain capacity, and high voltage at a selected level are needed for small-scale PV solar independent AC loads and for grid applications as well as. This study offers a step-up boost inverter with quadruple operation of 9-levels that solves the problem by using a switched capacitor approach with less complications. By utilizing the control scheme itself, the topology is intended to balance capacitor voltages without the requirement for sensors. A phase disposition- pulse width modulation (PD-PWM) control technique is employed in this topology. This work focuses on the switching operation modes of the anticipated inverter and presents experimentally confirmed simulation experiments carried out in MATLAB/Simulink. All things considered; this research presents a viable option for renewable energy systems that can assist in satisfying the demand for electricity while preserving the environment.

### \*Corresponding Author:

E-mail address: <a href="mailto:lois.david@earet.uniport.edu.ng">lois.david@earet.uniport.edu.ng</a> & <a href="mailto:lois.david@earet.uniport.edu.ng">lois.david@earet.edu.ng</a> & <a href="mailto:lois.david@earet.uniport.edu.ng">lois.david@earet.edu.ng</a> & <a href="mailto:lois.david@earet.uniport.edu.ng">lois.david@earet.uniport.edu.ng</a> & <a href="mailto:lois.david@earet.uniport.edu.

#### 1. INTRODUCTION

The global electricity demand is increasing rapidly, but the predominant means of electrical energy generation, such as the combustion of fossil fuels and nuclear materials, result in the emission of harmful gases that contribute to environmental imbalances on a global scale. To address this challenge, there is a growing interest in adopting renewable energy sources that are environmentally friendly. However, renewable energy generation stations are often situated at a considerable distance from load centers, resulting in amplified transmission and distribution losses during the delivery of electrical energy [1]-[3]. Rooftop distributed solar photovoltaic (PV) systems have been presented recently as a solution to this problem. These systems typically exhibit power and voltage ratings in the

range of 0.5 kW to 5 kW and 60-100 V, respectively. Rooftop PV systems are becoming increasingly popular, and the number of units is expected to reach 100 million by 2030, which could be achieved by maintaining today's yearly installation rate. Rooftop PV systems offer numerous benefits, including reduced transmission and distribution losses, lower capital and operational costs, and lower maintenance requirements. The paper suggests a modified nine-level inverter that achieves all of the aforementioned objectives with fewer components by using a switched capacitor approach. The topology is designed to balance capacitor voltages without the need for sensors, using the control scheme itself. A Phase disposition Pulse Width Modulation (PDPWM) is handled as the control scheme for the proposed topology. Overall, rooftop PV systems offer a promising solution for renewable energy systems that can help meet electricity demands while maintaining a clean and green environment [4].

The increasing demand for electrical energy is met by conventional energy sources, which harm the environment. To address this issue, renewable energy sources are becoming more popular. Installing distributed solar photovoltaic (PV) systems on rooftops has been a novel way to lower transmission and distribution losses when the power is transferring from various generation stations to local load centers [5]-[8]. In a step-up 9-level inverter employing a technique of switched capacitor (SC) and requires fewer components is proposed to address the challenges of rooftop PV systems. The topology is designed to balance capacitor voltages without the need for sensors, using the control scheme itself. The multilevel inverter (MLI) is a power conversion technology used in power electronics and renewable energy systems. The necessity of DC-AC conversion and high-gain DC-DC converters to match AC grid voltage levels is covered in the article. The various types, such as MLI's of diode-clamped, flying-capacitor [9]-[11], and cascaded H-bridge (CHB) [12]-[14] are also discussed along with the modifications made to lessen the reliance on isolated DC sources, address capacitor voltage balancing issues, and minimize the number of switches [15]-[18]. It is reported that the SC enabled MLIs are well-suited for RE system applications, including small scale solar PV rooftops [19].

A boost-SC inverter by arranging in a Marx structure manner that employs SC techniques to increase the number of output voltage levels [14]. The Marx structure units enhance the output voltage levels when added to the H-bridge. Other advancements in MLIs have been proposed in [16] to overcome challenges such as capacitor unbalancing, reduced switch count, and improved voltage levels. For example, a cascaded MLI using separate DC voltage sources for the front-end and back-end units has been proposed in [16]. Switched capacitor techniques are used by the front-end unit, while an H-bridge unit is used by the lateral end. The number of layers is increased by cascading these units together. Furthermore, a hybrid SC-MLI [17] consists of one capacitor, two complementary switches placed in parallel or series, and single DC voltage gives a greater number of levels of voltages.

Multilevel inverters (MLIs) frequently employ switched capacitor techniques to provide the desired output voltage levels. Several methods for designing MLIs with switched capacitor techniques have been put forth. To explain this, let us consider a voltage boost MLI of general purpose, which consists of number of series and parallel switches to the input and output points along diodes and capacitors [18]. As in the ref [19], one should note that the intended output voltage levels can be produced by an inductor incorporated into the resonance circuit of a quasi-resonant MLI. An arrangement of repeated switching capacitor units of cross-connection at the end of two T-type circuits is useful to find out the output voltage levels [19]-[23]. The work presented in [22] pacts a DC-source cascaded H- bridge MLI. Using switched capacitor techniques, output voltage levels are achieved by substituting isolated DC voltage sources with capacitors. Series/parallel conversion inverter for a hybrid nine-level inverter is introduced [23]. This inverter can increase voltage levels while passively balancing capacitor voltage to maintain a steady voltage. In [24], a generalized inverter topology with an active neutral point clamped (ANPC) gain1 is shown. By adding switches and capacitors, various voltage levels can be enabled. The authors of the work [23]-[26] are presented with a generic five-level inverter to increase the number of output voltage levels as compared to the earlier level inverters and which consists of four switches and a capacitor module.

Several novel multilevel inverter (MLI) topologies have been put forth in an effort to solve the problems that arise in applications involving renewable energy. The ref [25] demonstrates a hybrid T-type nine-level inverter with triple gain, in which it uses special arrangements of switches, diodes, and capacitors to provide the required voltage levels. Another invention that was introduced in [26] is the

generalized CGSC- TL architecture, which provides various configurations of switches, diodes, and capacitors to generate the required volt- age levels. By modifying the boost converter as an MLI using series/parallel combinations of switches, diodes, and capacitors, the CGT9L boost inverter—which was first announced in [27]—provides common grounding between the DC source and the output AC. Furthermore, the method discussed in the ref [28] creates output levels by fusing two units: an H-bridge unit and a generating unit with circuit components. A 7-level SC (7-LSC) architecture with gain-3 was introduced in [29], a MLI topology with switches of unipolar in bi-directional and bipolar in unidirectional direction was offered in [30]. Because the capacitors are naturally capable of self-balancing voltage, these topologies do not command sensor units to sense and assess the voltage between different capacitors [30]-[34]. This research concludes with the introduction of a new topology that has fewer components than current competitor topologies. The following points indicate the contributions of the manuscript:

- A 9-level SC based MLS topology is advised with a fewer number of switches and capacitors and simulated the same by utilizing MATLAB.

- A self-balancing scheme for capacitors is introduced with a phase disposition PWM control strategy.

#### 2. PROPOSED INVERTER TOPOLOGY

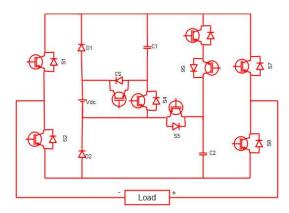

As shown in Figure 1, the inverter consists of mainly a source of DC voltage, capacitor numbers- two (C1, C2), and electronic switches of eight. One of the switches operates bidirectionally (S6), while the remaining seven switches function unidirectionally (S1to S8).

The switches S7, S8, S1, and S2 work together to prevent short-circuit damage between the source and capacitors. The C1 and C2 are charging and discharging in parallel and series with the DC voltage source ensures the desired output voltages. Particularly, self-balanced voltages across capacitors C1 and C2 are produced by charging and discharging them to  $\pm 1$ Vdc and  $\pm 2$ Vdc, respectively. Across the load, the output voltage levels can be  $\pm 1$  to  $\pm 4$  Vdc. Capacitors are charged and discharged using the earlier stated techniques of parallel/series, which guarantee capacitors in balanced mode and achieve the desired voltage levels using a single DC source via a precise switching pattern. To generate all voltage levels except zero, a total of six switches are continually toggled ON in conjunction with the discharged capacitor. To reach zero, turn on the 2 switches on the upper/positive sign arm or the lower/negative sign arm.

Figure 1. Architecture of proposed 9-level MLI.

# 2.1 Operating modes:

# A. Zero Voltage Levels:

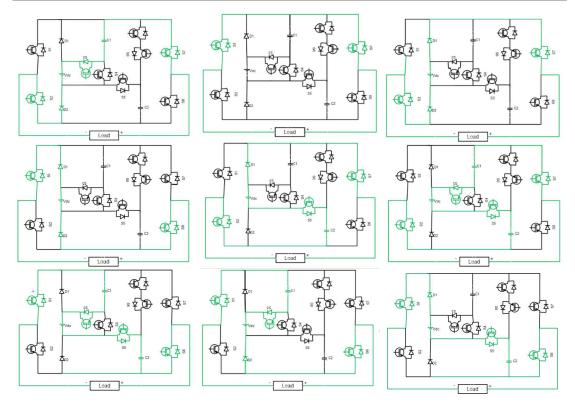

In this work, two approaches for reaching the zero-voltage level with the suggested topology: either by turn-on the lower arm switches (S8, S2) or by the upper arm switches (S7, S1). The creation of the 0 V level utilizing the upper side arm switches is shown in Figure 2(a).

### B. Positive Voltage Levels:

To achieve the different voltage levels in the proposed topology, specific switches are activated in a particular sequence. The following describes the activation of switches to generate each voltage level:

Voltage Level of +1Vdc: The switches, S7 and S2 are activated to establish a series connection between the DC voltage source and the load. Simultaneously, switch S4 is engaged to facilitate the charging of capacitor C1 to +1Vdc. The C2 is left in a floating state (-), refraining from both charging and discharging. This arrangement ensures the transmission of +1Vdc to the load, as depicted in Fig 2(b).

Voltage Level of +2Vdc: The switches, S3, S7, and S2 are employed to create a series alignment among the DC voltage, capacitor C1, and the load. Additionally, switch S3 is activated to discharge capacitor C1 to +1Vdc, while switch S6 is turned on to charge capacitor C2 to +2Vdc. The outcome is the transmission of +2Vdc to the load, as illustrated in Fig 2(c).

Voltage Level of +3Vdc: The switches S2, S7, and S5 are activated to establish a series connection between DC voltage, capacitor C2, and the load. Concurrently, switch S5 is turned on to discharge capacitor C2 to +2Vdc. Meanwhile, capacitor C1 remains in a floating state (-), without undergoing charging or discharging. This configuration enables the transmission of +3Vdc to the load, as shown in Fig 2(d).

Voltage Level of +4Vdc: The S3, S7, S2, and S5 are activated to establish a series connection among the DC voltage, capacitor C1, capacitor C2, and the load. Switch S3 is then turned on to discharge capacitor C1 to +1Vdc, while switch S4 is activated to discharge capacitor C2 to +2Vdc. In this scenario, both capacitors release their stored energy, resulting in the transmission of +4Vdc to the load, as depicted in Fig 2(e).

### C. Negative Voltage Levels:

To achieve negative voltage levels in the proposed topology, specific switches are activated in a particular sequence. The following describes the activation of switches to generate each negative voltage level: -1Vdc Voltage Level: Switches S1, S8, and S2 are activated to establish a series connection between the DC voltage source and the load. Additionally, switch S4 is engaged to charge capacitor C1 to +1Vdc, while capacitor C2 is maintained in a floating state (-), devoid of charging or discharging. This configuration facilitates the transmission of -1Vdc to the load, as depicted in Fig 2(f).

Voltage Level of -2Vdc: Switches S3, S8, and S2 are turned on to create a series arrangement involving the DC voltage source, capacitor C1, and the load. Furthermore, switch S3 is activated to discharge capacitor C1 to +1Vdc, and switch S6 is turned on to charge capacitor C2 to +2Vdc. This results in the transmission of - 2Vdc to the load, as illustrated in Fig 2(g).

Voltage Level of -3Vdc: Activation of switches S1, S8, and S5 establishes a series connection among the DC voltage source, capacitor C2, and the load. Simultaneously, switch S5 is turned on to discharge capacitor C2 to +2Vdc, while capacitor C1 is kept in a floating state (-) without undergoing charging or discharging. This arrangement enables the transmission of -3Vdc to the load, as shown in Figure 2(h).

Voltage Level of -4Vdc: The S3, S8, and S5 are activated to establish a series connection involving the DC voltage source, capacitor C1, capacitor C2, and eight triangular carriers and the load. Additionally, switch S3 is turned on to discharge the C1 to +1Vdc, and switch S4 is activated to discharge capacitor C2 to +2Vdc. In this scenario, these two capacitors to deliver their earlier stored energy, resulting in the transmission of -4Vdc to the load, as indicated in Figure 2(i).

Figure 2. Operating modes of the 9-level MLI.

## 3. METHODOLOGY

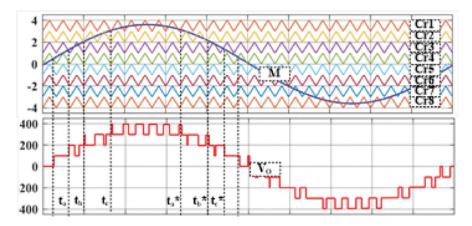

The implementation utilizes level shifted- PWM (LS- PWM) to generate switching pulses. In this technique, the number of required carrier signals equal to the number of required level of output voltage minus one. The schema of level-shifted PWM is shown in Figure 3.

The LS-PWM employs a single sinusoidal modulating signal ( $M = Vmsin (2\pi fmt)$ ) signals (Cr1 - Cr8). The com- parison between the modulating signal and carrier signals generates eight pulses (X1 - X8). During positive cycles, X1 compares M with Cr1, followed by X2 comparing M with Cr2, and so forth. Conversely, during negative cycles, X8 represents the comparison with Cr8, while X7 compares with Cr7, and so on. A switching table, as outlined in Table 1, establishes the logic pattern to generate appropriate switching pulses for the switches. One should note that the value of carrier signal amplitude remains constant, while the modulation signal amplitude adjusting from 0 to 4, facilitating the generation of various modulation index values (Ma = 0.4, 0.7, and 0.9).

| Switches (S1 to S8) | +4Vdc | +3Vdc | +2Vdc | +Vdc | 0 Vdc | -Vdc | -2Vdc | -3Vdc | -4Vdc |

|---------------------|-------|-------|-------|------|-------|------|-------|-------|-------|

| 1                   | 0     | 0     | 0     | 0    | 1     | 1    | 1     | 1     | 1     |

| 2                   | 1     | 1     | 1     | 1    | 0     | 0    | 0     | 0     | 0     |

| 3                   | 1     | 0     | 1     | 0    | 0     | 0    | 1     | 0     | 1     |

| 4                   | 0     | 1     | 0     | 1    | 0     | 1    | 0     | 1     | 0     |

| 5                   | 1     | 1     | 0     | 0    | 0     | 0    | 0     | 1     | 1     |

| 6                   | 0     | 0     | 1     | 0    | 0     | 0    | 1     | 0     | 0     |

| 7                   | 1     | 1     | 1     | 1    | 1     | 0    | 0     | 0     | 0     |

| 8                   | 0     | 0     | 0     | 0    | 0     | 1    | 1     | 1     | 1     |

Table 1. ON and OFF Stages of Switching stages.

For a given value of Ma, the frequency of modulating signal resides at a constant, while the frequency of carrier signal varies between the frequencies of 125 Hz, 150 Hz, and 200 Hz to align with the load frequency of 50Hz. Increasing the carrier signal frequency raises harmonic levels; however, to mitigate switching losses, the carrier frequency is limited to 5 KHz.

Figure 3. Schema of level-shifted PWM.

The estimation of capacitance values is imperative and that ensures the desired voltage of output under-appreciated ripple values. The output voltage levels are determined by the amount of capacitor energy, which includes charging and discharging. As illustrated in Fig. 3, the calculations procedure for capacitance values are considered by considering the maximum discharging intervals. The capacitor C1 is designed to deliver the  $\pm 2V$  dc and  $\pm 4V$  dc, while the capacitor C2 discharges at a value of ±3V dc and ±4V dc. As shown in Fig 3, the switching transitions, i.e., ta, tb, tc, ta\*, tb\*, and tc\*for each voltage level are calculated by (1) - (6) [30]-[32].

$$t_{a} = \frac{\sin^{-1}\frac{1}{4}}{\omega_{m}}$$

$$t_{b} = \frac{\sin^{-1}\frac{2}{4}}{\omega_{m}}$$

$$t_{c} = \frac{\sin^{-1}\frac{3}{4}}{\omega_{m}}$$

(1)

(2)

$$t_b = \frac{\sin^{-1}\frac{2}{4}}{\omega_m} \tag{2}$$

$$t_c = \frac{\sin^{-1}\frac{3}{4}}{\omega_m} \tag{3}$$

$$t_a^* = \frac{\pi - \sin^{-1}\frac{1}{4}}{\omega_m} \tag{4}$$

$$t_b^* = \frac{\pi - \sin^{-1}\frac{2}{4}}{\omega_m} \tag{5}$$

$$t_c^* = \frac{\pi - \sin^{-1}\frac{3}{4}}{\omega_m} \tag{6}$$

Under resistive load circumstances, the highest discharging occurs at the  $\pm 4V$  dc voltage level. A substantial amount of voltage decline occurs within the time interval (tx - ty). When determining the capacitance values, careful consideration is given to extended discharging time intervals for each capacitor. It is noted that the charge or discharge cycles can occur multiple times within the (tx - ty) interval. The discharging time intervals for capacitor C1 are denoted as (tx1 - ty)tx2), while the corresponding intervals for capacitor C2 are expressed as (ty1 - ty2).

### 4. RESULTS AND DISCUSSIONS

The merit of the present configuration can be substantiated through simulation outcomes, considering various component parameters under diverse load conditions. Specifically, the input fix at 100V DC, and the capacitor values are designated as C1 = 2200  $\mu F$  and C2 = 2200  $\mu F$ . The load at end side is as RL = 100ohm + 150mH with a Ma value of 1. Fig 4 indicates (from top to bottom) the MATLAB results of output responses such as voltages and currents. Figures 4 and 5 represent simulation results corresponding to output voltage, current and capacitor voltages under RL load and the switching frequency variations.

| Parameters            | References |      |      |      |      |      |      |      |      |      |              |      |       |          |

|-----------------------|------------|------|------|------|------|------|------|------|------|------|--------------|------|-------|----------|

|                       | 2012       | 2013 | 2014 | 2014 | 2017 | 2018 | 2019 | 2021 | 2021 | 2022 | 2022         | 2022 | 2022  | Proposed |

|                       | [14]       | [15] | [16] | [17] | [18] | [19] | [20] | [24] | [25] | [26] | [27]         | [28] | [29]  |          |

| Ns                    | 1          | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1            | 1    | 1     | 1        |

| Nsw                   | 13         | 12   | 8    | 10   | 10   | 17   | 18   | 12   | 14   | 9    | 12           | 10   | 11    | 8        |

| N-drivers             | 13         | 12   | 8    | 10   | 10   | 17   | 18   | 11   | 14   | 9    | 12           | 10   | 11    | 8        |

| ND                    | 0          | 2    | 6    | 3    | 4    | 0    | 5    | 2    | 0    | 2    | 1            | 0    | 0     | 2        |

| NC                    | 3          | 2    | 3    | 3    | 3    | 4    | 4    | 4    | 5    | 5    | 2            | 2    | 2     | 2        |

| G                     | 4          | 4    | 4    | 4    | 4    | 1    | 4    | 3    | 4    | 4    | 4            | 4    | 3     | 4        |

| MBV                   | 4          | 4    | 4    | 4    | 4    | 4    | 4    | 3    | 4    | 2    | 4            | 4    | 3     | 4        |

| TSV                   | 6.25       | 6.25 | 8    | 6.25 | 7.5  | 7.25 | 7    | 7.5  | 7.5  | 10   | 7.5          | 6.25 | 5.53  | 6.25     |

| N-total               | 16         | 16   | 17   | 16   | 18   | 21   | 27   | 18   | 19   | 16   | 14           | 12   | 13    | 12       |

| No. of voltage levels | 9          | 9    | 9    | 9    | 9    | 9    | 9    | 9    | 9    | 9    | 9            | 9    | 7     | 9        |

| Efficiency (%)        | 85.9       | 83   | 91.5 | 91.6 | 93.5 | NA   | 92.5 | 94.5 | 98.3 | 94   | 87 -<br>95.5 | 97   | 98.77 | 96.5     |

Table 2. Comparison of proposed work.

Table 2 provides a comprehensive comparison of various parameters across multiple references in the literature. The parameters include Ns (no. of stages), N-sw (no. of switches), N-drivers (no. of drivers), ND (no. of diodes), NC (no. of capacitors), G (Gain), MB (Minimum breakdown voltage), TSV (Total simulation time in milliseconds), N-Total (Total number of components), Number of Voltage Levels, and Efficiency (%). Each parameter is compared across different references spanning from 2012 to proposed solutions, with corresponding numerical values provided for each reference year. The table offers insights into the evolution and performance variations of different solutions over time, allowing researchers and practitioners to analyze trends and make informed decisions regarding the selection and optimization of circuit designs. Additionally, the efficiency percentages provide an indication of the overall effectiveness of the solutions, with higher values suggesting improved performance and energy utilization. This comparative analysis aids in identifying potential areas for further research and improvement in the design and implementation of electrical circuits.

The proposed configuration exhibits the capability to elevate the input voltage from 100V to 400V as voltage at output while maintaining equilibrium in capacitor voltages with C1 at 100V and C2 at 200V. The voltage THD of the output is recorded below 5%.

Figure 4. Output responses of (a) voltage, (b) current and (c) capacitor for RL load.

Figure 5. Output responses (top to bottom) of output voltage, current and capacitor voltage across capacitors.

## **5. CONCLUSION**

This article introduces a brand-new nine-level inverter with a single DC supply that is intended for standalone solar PV installations. The suggested topology uses a parallel/series-charging/discharging method for capacitors and boasts quadruple voltage gain capabilities. The voltages of capacitors are balanced using LSPWM to produce the desired output voltage with the least amount of component stress. This topology's experimental setup can be adjusted to accommodate a range of situations, such as changing load scenarios, variation of input voltage,

switching frequency, changes in amplitude and frequency modulation and frequency adjustments. Both the output voltage's THD and the capacitors' voltage ripples fall well within permissible bounds of 5%. A comparative study shows that the suggested topology has a simple structure, fewer switches, the ability to boost quadruple, improved efficiency, affordability, and a lower Total Switching Stress (T.S.V). Results from MATLAB simulations support the effectiveness of the suggested design. Essentially, this novel topology provides a single DC source power solution for renewable solar PV applications that need triple voltage gain DC-AC power conversion and less switch- ing stress from fewer switches. The current work can be extended to emerging areas of RES and electric vehicles [35]-[37].

#### DECLARATIONS

**Conflict of Interest:** The authors declare that there is no conflict of interests.

Funding: This research received no external funding.

Availability of data and materials: No data is available in this article.

**Publisher's note:** The Journal and Publisher remain neutral with regard to jurisdictional claims in published maps and institutional affiliations.

### **REFERENCES:**

- [1]. Solanke, Aman Vaijnath, Suman Kumar Verma, Satyam Kumar, Benneth Oyinna, and Kenneth E. Okedu. "MPPT For Hybrid Energy System Using Machine Learning Techniques." *Journal of Modern Technology* (2024): 19-37.

- [2]. Panigrahi, Ramanuja, Santanu K. Mishra, Suresh C. Srivastava, Anurag K. Srivastava, and Noel N. Schulz. "Grid integration of small-scale photovoltaic systems in secondary distribution network—A review." *IEEE Transactions on Industry Applications* 56, no. 3 (2020): 3178-3195. DOI: 10.1109/TIA.2020.2979789

- [3]. Ramesh, Bhukya, Gauri Suhashini, B. V. V. N. Kalnoor, and D. Nageswara Rao. "Cost Optimization by Integrating PV-System and Battery Energy Storage System into Microgrid using Particle Swarm Optimization." *International Journal of Pure and Applied Mathematics* 114, no. 8 (2017): 45-55.

- [4]. Gupta, Krishna Kumar, Alekh Ranjan, Pallavee Bhatnagar, Lalit Kumar Sahu, and Shailendra Jain. "Multilevel inverter topologies with reduced device count: A review." *IEEE transactions on Power Electronics* 31, no. 1 (2015): 135-151. DOI: 10.1109/TPEL.2015.2405012

- [5]. Bana, Prabhat Ranjan, Kaibalya Prasad Panda, R. T. Naayagi, Pierluigi Siano, and Gayadhar Panda. "Recently developed reduced switch multilevel inverter for renewable energy integration and drives application: topologies, comprehensive analysis and comparative evaluation." *IEEE access* 7 (2019): 54888-54909. DOI: 10.1109/ACCESS.2019.2913447

- [6]. Salem, Ahmed, Huynh Van Khang, Kjell G. Robbersmyr, Margarita Norambuena, and Jose Rodriguez. "Voltage source multilevel inverters with reduced device count: Topological review and novel comparative factors." *IEEE transactions on power electronics* 36, no. 3 (2020): 2720-2747. DOI: 10.1109/TPEL.2020.3011908

- [7]. Sandeep, N., and Udaykumar R. Yaragatti. "Operation and control of an improved hybrid nine-level inverter." *IEEE Transactions on industry applications* 53, no. 6 (2017): 5676-5686. DOI: 10.1109/TIA.2017.2737406

- [8]. Sandeep, N., and Udaykumar R. Yaragatti. "A switched-capacitor-based multilevel inverter topology with reduced components." *IEEE Transactions on Power Electronics* 33, no. 7 (2017): 5538-5542. DOI: 10.1109/TPEL.2017.2779822

- [9]. Srndovic, Milan, Aidar Zhetessov, Tohid Alizadeh, Yakov L. Familiant, Gabriele Grandi, and Alex Ruderman. "Simultaneous selective harmonic elimination and THD minimization for a single-phase multilevel inverter with staircase modulation." *IEEE Transactions on Industry Applications* 54, no. 2 (2017): 1532-1541. DOI: 10.1109/TIA.2017.2775178

- [10]. Espinosa, Eduardo E., Jose R. Espinoza, Pedro E. Melín, Roberto O. Ramírez, Felipe Villarroel, Javier A. Muñoz, and Luis Morán. "A new modulation method for a 13-level asymmetric inverter toward

- minimum THD." IEEE Transactions on Industry Applications 50, no. 3 (2013): 1924-1933. DOI: 10.1109/TIA.2013.2282494

- [11]. Panda, Kaibalya Prasad, Prabhat Ranjan Bana, and Gayadhar Panda. "FPA optimized selective harmonic elimination PWM technique application in reduced switch count multilevel inverter." In 2018 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), pp. 1-6. IEEE, 2018. DOI: 10.1109/PEDES.2018.8707792

- [12]. Kumari, Manita, Marif Daula Siddique, Adil Sarwar, Mohd Tariq, Saad Mekhilef, and Atif Iqbal. "Recent trends and review on switched-capacitor-based single-stage boost multilevel inverter." *International Transactions on Electrical Energy Systems* 31, no. 3 (2021): e12730. DOI: https://doi.org/10.1002/2050-7038.12730

- [13]. Barzegarkhoo, Reza, Mojtaba Forouzesh, Sze Sing Lee, Frede Blaabjerg, and Yam P. Siwakoti. "Switched-capacitor multilevel inverters: A comprehensive review." *IEEE Transactions on Power Electronics* 37, no. 9 (2022): 11209-11243. DOI: 10.1109/TPEL.2022.3164508

- [14]. Hinago, Youhei, and Hirotaka Koizumi. "A switched-capacitor inverter using series/parallel conversion with inductive load." *IEEE Transactions on industrial electronics* 59, no. 2 (2011): 878-887. DOI: 10.1109/TIE.2011.2158768

- [15]. Liu, Junfeng, Ka Wai Eric Cheng, and Yuanmao Ye. "A cascaded multilevel inverter based on switched-capacitor for high-frequency AC power distribution system." *IEEE transactions on power* electronics 29, no. 8 (2013): 4219-4230. DOI: 10.1109/TPEL.2013.2291514

- [16]. Babaei, Ebrahim, and Saeed Sheermohammadzadeh Gowgani. "Hybrid multilevel inverter using switched capacitor units." *IEEE Transactions on industrial electronics* 61, no. 9 (2013): 4614-4621. DOI: 10.1109/TIE.2013.2290769

- [17]. Ye, Yuanmao, Ka Wai Eric Cheng, Junfeng Liu, and Kai Ding. "A step-up switched-capacitor multilevel inverter with self-voltage balancing." *IEEE Transactions on industrial electronics* 61, no. 12 (2014): 6672-6680. DOI: 10.1109/TIE.2014.2314052

- [18]. Zeng, Jun, Jialei Wu, Junfeng Liu, and Huafang Guo. "A quasi-resonant switched-capacitor multilevel inverter with self-voltage balancing for single-phase high-frequency AC microgrids." *IEEE Transactions on Industrial Informatics* 13, no. 5 (2017): 2669-2679. DOI: 10.1109/TII.2017.2672733

- [19]. Khenar, Mohammad, Amir Taghvaie, Jafar Adabi, and Mohammad Rezanejad. "Multi-level inverter with combined T-type and cross-connected modules." *IET Power Electronics* 11, no. 8 (2018): 1407-1415. DOI: <a href="https://doi.org/10.1049/iet-pel.2017.0378">https://doi.org/10.1049/iet-pel.2017.0378</a>

- [20]. Jahan, Hossein Khoun, Mehdi Abapour, and Kazem Zare. "Switched-capacitor-based single-source cascaded H-bridge multilevel inverter featuring boosting ability." *IEEE Transactions on Power Electronics* 34, no. 2 (2018): 1113-1124. DOI: 10.1109/TPEL.2018.2830401

- [21]. Nakagawa, Yuya, and Hirotaka Koizumi. "A boost-type nine-level switched capacitor inverter." *IEEE Transactions on Power Electronics* 34, no. 7 (2018): 6522-6532. DOI: 10.1109/TPEL.2018.2876158

- [22]. Lee, Sze Sing, Chee Shen Lim, and Kyo-Beum Lee. "Novel active-neutral-point-clamped inverters with improved voltage-boosting capability." *IEEE Transactions on Power Electronics* 35, no. 6 (2019): 5978-5986. DOI: 10.1109/TPEL.2019.2951382

- [23]. Siddique, Marif Daula, Bhimireddy Prathap Reddy, Atif Iqbal, and Saad Mekhilef. "Reduced switch count-based N-level boost inverter topology for higher voltage gain." *IET Power Electronics* 13, no. 15 (2020): 3505-3509. DOI: <a href="https://doi.org/10.1049/iet-pel.2020.0359">https://doi.org/10.1049/iet-pel.2020.0359</a>

- [24]. Dhara, Sumon, and V. T. Somasekhar. "A nine-level transformerless boost inverter with leakage current reduction and fractional direct power transfer capability for PV applications." *IEEE journal of emerging and selected topics in power electronics* 10, no. 6 (2021): 7938-7949. DOI: 10.1109/JESTPE.2021.3074701

- [25]. Barzegarkhoo, Reza, Sze Sing Lee, Shakil Ahamed Khan, Yam P. Siwakoti, and Dylan Dah-Chuan Lu. "A novel generalized common-ground switched-capacitor multilevel inverter suitable for transformerless grid-connected applications." *IEEE Transactions on Power Electronics* 36, no. 9 (2021): 10293-10306. DOI: 10.1109/TPEL.2021.3067347

- [26]. Lee, Sze Sing, Yam P. Siwakoti, Reza Barzegarkhoo, and Frede Blaabjerg. "A novel common-ground-type nine-level dynamic boost inverter." *IEEE Journal of Emerging and Selected Topics in Power Electronics* 10, no. 4 (2021): 4435-4442. DOI: 10.1109/JESTPE.2021.3104939

- [27]. Varesi, Kazem, Fatemeh Esmaeili, Saeid Deliri, and Hadi Tarzamni. "Single-input quadruple-boosting switched-capacitor nine-level inverter with self-balanced capacitors." *IEEE Access* 10 (2022): 70350-70361. DOI: 10.1109/ACCESS.2022.3187005

- [28]. Singh, Ashutosh Kumar, Ravi Raushan, Rajib Kumar Mandal, and Md Waseem Ahmad. "A new single-source nine-level quadruple boost inverter (nqbi) for pv application." *IEEE Access* 10 (2022): 36246-36253. DOI: 10.1109/ACCESS.2022.3163262

- [29]. Singh, Ashutosh Kumar, Rajib Kumar Mandal, and Ravi Anand. "Quasi-resonant switched-capacitor-based seven-level inverter with reduced capacitor spike current." *IEEE Journal of Emerging and Selected Topics in Power Electronics* 11, no. 2 (2022): 1953-1965. DOI: 10.1109/JESTPE.2022.3224536

- [30]. Krishna, B. Murali, V. V. Sandeep, and Rupa Rani. "Design and simulation of voltage sensor-based electronic load balance controller for SEIG based isolated load applications." *Jour of Adv Research in Dynamical & Control Systems* 12, no. 3 (2020): 345-352. DOI: 10.5373/JARDCS/V12I3/20201200

- [31]. Falehi, Ali Darvish. "Novel chattering free binomial hyperbolic sliding mode controller for asymmetric cascaded E-type bonded T-type multilevel inverter-based dynamic voltage restorer to meliorate FRT capability of DFIG-based wind turbine." *Results in Engineering* 23 (2024): 102370. DOI: <a href="https://doi.org/10.1016/j.rineng.2024.102370">https://doi.org/10.1016/j.rineng.2024.102370</a>

- [32]. S Patthi, V. B Murali Krishna, L Reddy, S Arandhakar, "Photovoltaic String Fault Optimization Using Multi-Layer Neural Network Technique" Results in Engineering, Volume 22, June 2024, 102299. DOI: https://doi.org/10.1016/j.rineng.2024.102299

- [33]. Mopidevi Subbarao, Kiransai Dasari, SSSR Sarathbabu Duvvuri, KRKV Prasad, BK Narendra, VB Murali Krishna, "Design, control and performance comparison of PI and ANFIS controllers for BLDC motor driven electric vehicles", Measurement: Sensors, Volume 31, 101001, Feb 2024, DOI: <a href="https://doi.org/10.1016/j.measen.2023.101001">https://doi.org/10.1016/j.measen.2023.101001</a>

- [34]. S. Kovvali, N. Jayaram, S. V. K. Pulavarthi, Y. R. Shankar, J. Rajesh and V. G. Prasant, "Quadruple Boost Switched Capacitor-Based Inverter for Standalone Applications," in *IEEE Access*, vol. 11, pp. 30442-30458, 2023, DOI: 10.1109/ACCESS.2023.3260257.

- [35]. A. Poorfakhraei, M. Narimani and A. Emadi, "A Review of Multilevel Inverter Topologies in Electric Vehicles: Current Status and Future Trends," in *IEEE Open Journal of Power Electronics*, vol. 2, pp. 155-170, 2021, DOI: 10.1109/OJPEL.2021.3063550.

- [36]. Kumar, P. Sai Sampath, P. Suresh, and D. Lenine. "Performance improvement of predictive voltage control for interlinking converters of integrated microgrid." *Measurement: Sensors* 33 (2024): 101196. DOI: https://doi.org/10.1016/j.measen.2024.101196

- [37]. Kumar, Devineni Gireesh, Nagineni Venkata Sireesha, Neerudi Bhoopal, Ranjith Kumar Gatla, Hossam Kotb, Kareem M. AboRas, Ali Elrashidi, Mohammed Alqarni, Yazeed Yasin Ghadi, and Adel Oubelaid. "Application of soft computing algorithms for hybrid modular multilevel inverters." *Measurement:* Sensors 31 (2024): 100999. DOI: <a href="https://doi.org/10.1016/j.measen.2023.100999">https://doi.org/10.1016/j.measen.2023.100999</a>